| Unfinished |

EPMC1200/EPSC1200 Upgrade (2006~)

With some members replaced.

unfinished yet. |

|

|

2003 FPGA version

Early 2005 ASIC version

|

EPMC1100 (EPON(Ethernet Passive Optical Network) Master Controller Chip) used with EPSC1100

- about 10 people involved in EPMC and EPSC chipset developement

including board and S/W. The chipset also underwent system test using E-OLT and S-OLT system.

- My job in EPMC1100 ASIC (chip set):

- EPMC's MAC Control and PON Bridge Design : MAC Control(Up/Down mux/demux,

DBA, Auto-discovery of ONUs)

and PON Bridge(MAC and LLID lookup/learning/forwarding, VID-LLID mapping, ageing support). revision on part of MAC block.

- master-slave top simulation(wrote CPU processes for discovery, gate generation, various traffic generation/analysis, event generation).

- top integration, synthesis, P&R for EPMC FPGA(2002-2003) and top integration, synthesis, rtl/pre/post-simulation for EPMC ASIC(2003-2005).

- some driver works : initial test driver for VxWorks, support for Linux driver and CLI

- EPON master card for E-OLT and S-OLT System : I've also designed FPGA/ASIC based EPON master card for E-OLT and S-OLT system(PMA,PMD part was co-designed by Hyun-Kyun Choi in our team).

- The FPGA version was used in service demonstration in the city of Gwangjoo for more than 100 subscribers including offices and was used in ETRI's internal service. As of Dec. 2006, the ASIC version is being used in commercial service for about 1500 subscribers in the city of Gwangjoo.

EPMC ASIC can process 2 EPON links and each port can control upto 64 ONT/ONUs.

|

|

|

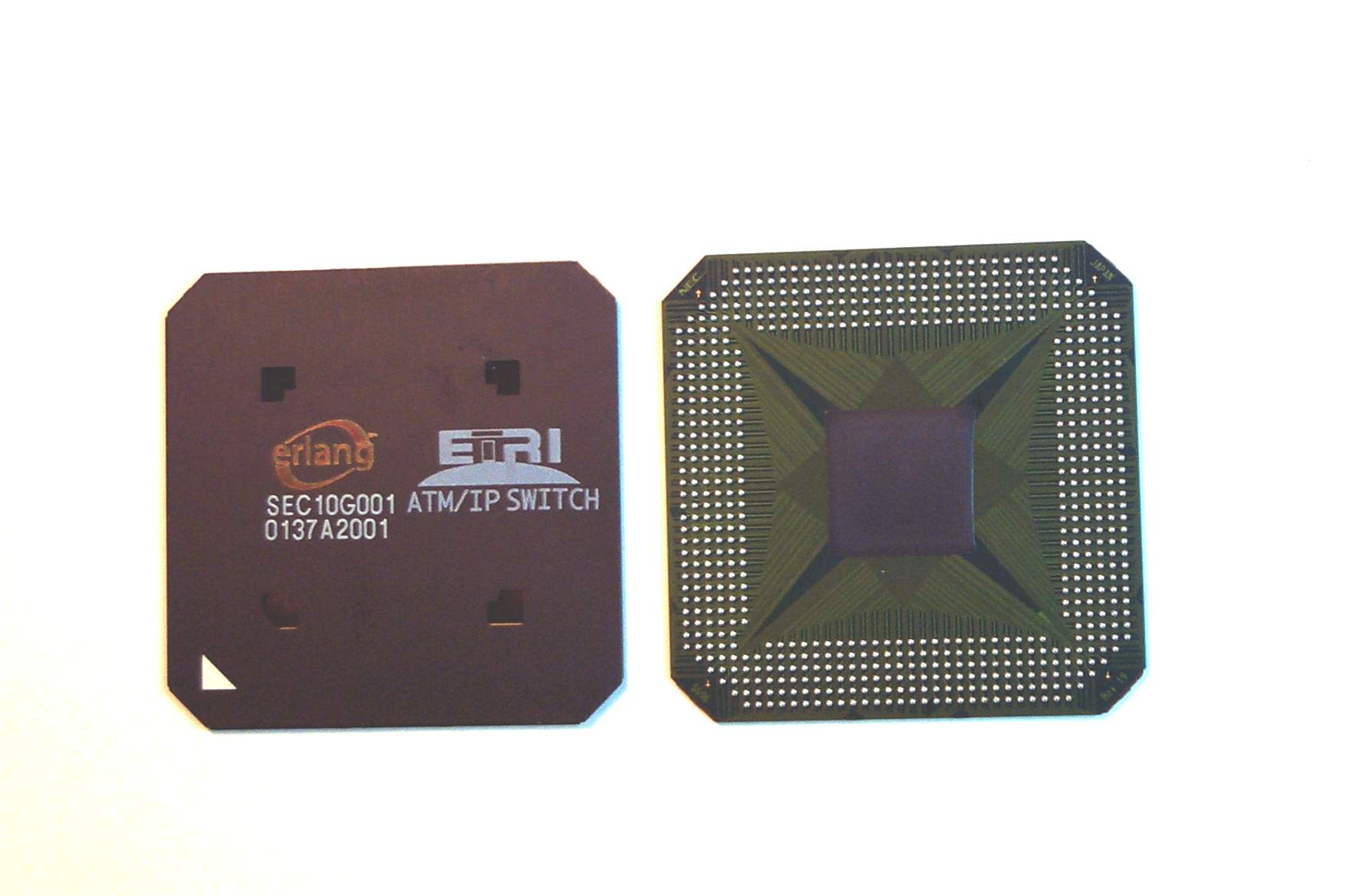

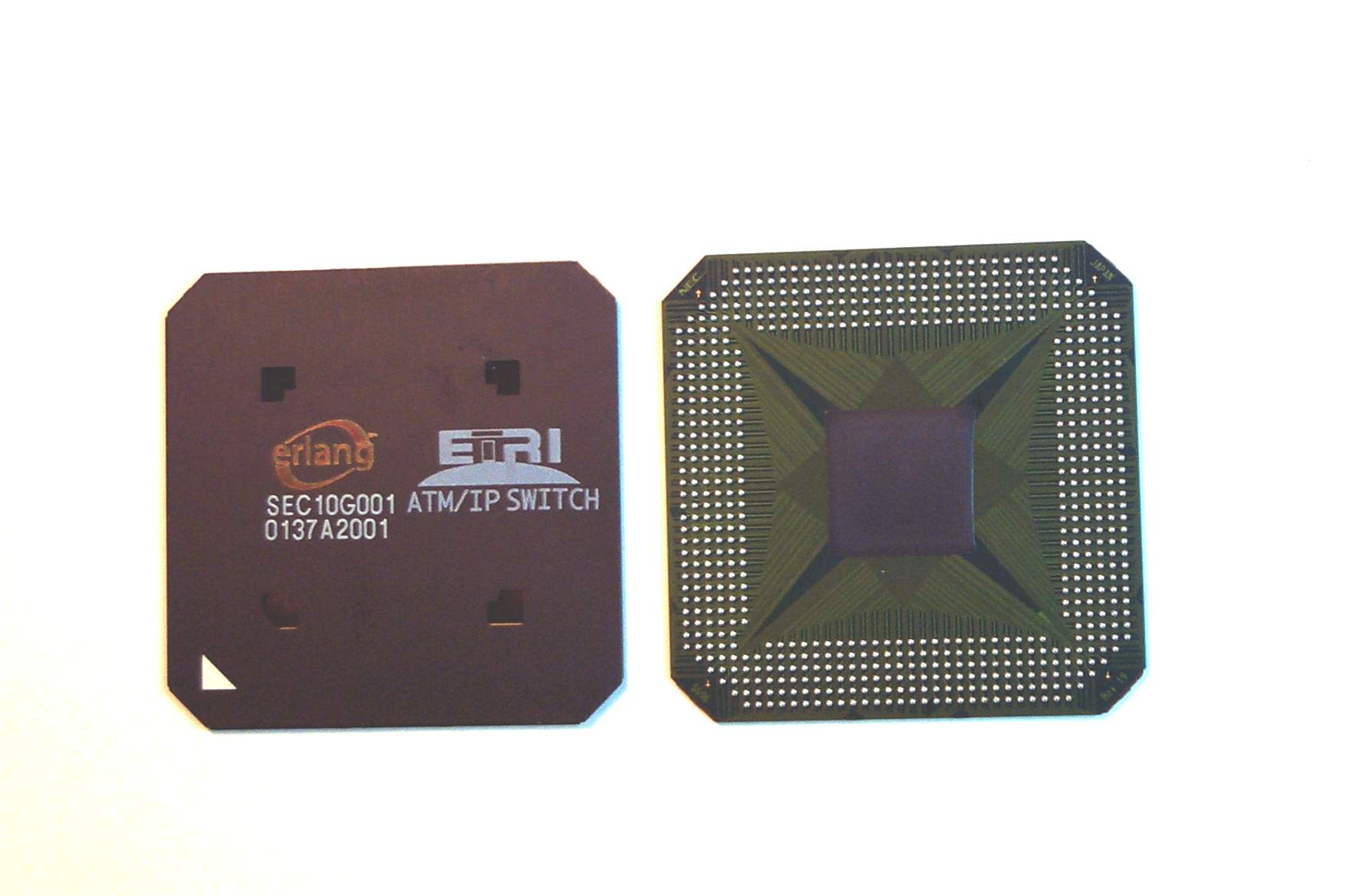

SE-C (10Gbps

Variable Length Packet Shared Memory Switch Chip, also called SIAN-1 or SE-1 chip ) :

Joint Project with Erlang Technology('99.9 - 2000.5, in St.

Louis MO. USA) :

- 16x16 shared memory packet switch. port speed is 800 Mbps.

- My Job : designed the main pointer processing path(see block diagram). It was used in Low-cost

Optical Subscriber Access System developed in ETRI.

- The chip was adopted and is being used in LG Electronics' commercial IMT-2000 switch system.

- 20Gbps Switch Fabric Card for ATM OLT System : I've developed 20Gbps through-put variable

legnth packet(including ATM cell) switch board for

Low-cost OLT system(POLS) using the SE-C chip and

Xilinx FPGAs. picture of the board

|

|

|

APSC ( ATM PON

slave chip)('99) used with APMC :

- alone.(also setup the master-slave top simulation, the master chip's developemnt had started almost 2 years earlier)

- my job : frame,ranging,message,lookup,cell processing and master-slave top simulation

- Many of the main functions(ranging,upstream downstream

cell transport) were verified. It was used in

Low-cost Optical Subscriber Access System now being

developed in ETRI.

- Hyndai 0.5um gate array, 100,000 gates.

|

|

|

SMC-01,02,03

( VDSL Modem ASICs) : (a take-over job)

- TC layer take-over(from MinHo Choi)and finishing work

(for three months in '98 and revision in 1999)

- My Job : debugging, redesign for some parts and verification for

the whole chip(SMC01,SMC03).

- They were used in MAIN-ONU

and set-top box. These VDSL chip sets use downstream QAM

and upstream QPSK modulation and uses Reed-Solomon coding

for error correction.

- Samsung 0.6um standard cell

|

|

|

ASAH-L4

(622Mbps ATM Layer ASIC ) (first in '98 and revision in

'99) :

- with another colleague(SangHo Lee).

- my job : I mainly did OAM,

routing control, output control, QOS buffering and memory

arbiter/interface and top simulation. The chip handles thousands of ATM

connections with routing, OAM, UPC, linked list based Shared QoS buffering and

ABR, multicast capabilities.

- It was used in Access Node

System (in both MAIN-OLT and MAIN-ONU systems) and

being used in Low-cost PON-based subscriber access

system(POLS & PPOS).

- Hyundai(LG) 0.35 Standard cell,

450,000 gates, 420 ball BGA.

|

|

|

ASAH-NIC (

155Mbps ATM SAR Layer Processing ASIC with PCI interface

and internal framer)('97) :

- with 2 other colleagues(JongArm Jun,Yeongho Park).

- My Jobs : I was

in charge of PCI core interface, DMA, segmentation(with

scheduling), memory arbiter/interface and top simulation, SCAN test.

- The chip can

process segmentation and reassembly for hundreds of

connections at the same time.

Linked list shared buffer is used for external cell

memory and CPU's packet memory.

There's no limitation in

the packet buffer in alignment, size and single packet

can be spread in multiple buffers both in segmentation

and reassembly.

- It was used in ATMgate adaptor card in

HANS system, and in another set-top box designed by

ImpressTech.

- LSI 0.5um LCB500K standard cell, 250,000

gates, 304pin PQFPt.

|

|

|

ASAH-P4

(622Mbps ATM Physical Layer ASIC) (first in '96(LSI Logic PGA) and

revision in '98(Samsung PQFP)) :

- alone. It was a modification from a former 155Mbps

design(mainly STM-1 to STM-4-4c and to 16 bit UTOPIA I/F).

- It was used in Access Node System(MAIN-AN and MAIN-ONU).

- Samsung 0.6um gate array, 110,000 gates. 208pin PQFP.

|

|